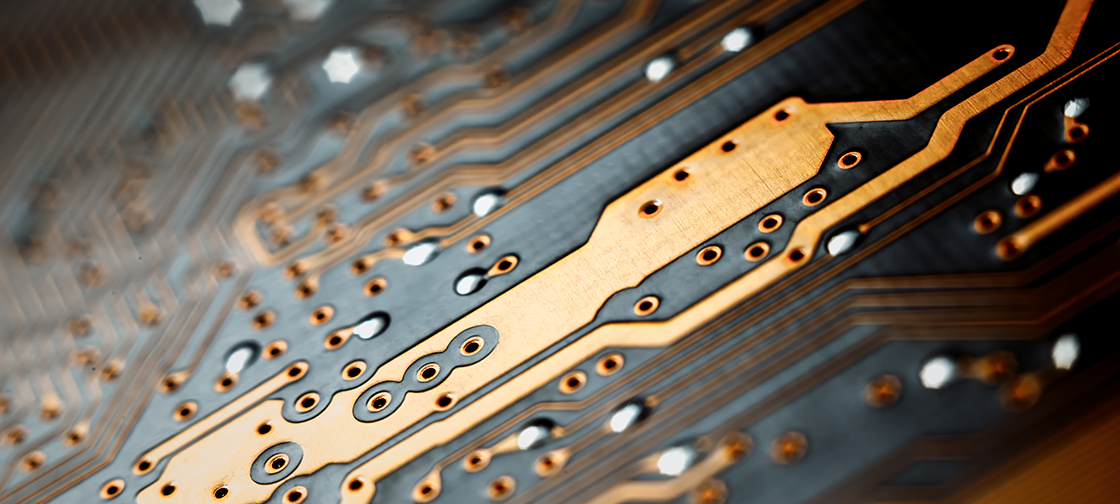

Silicon integrated circuits, which are used in computer processors, are approaching the maximum feasible density of transistors on a single chip—at least, in two-dimensional arrays.

Now, a team of engineers at the University of Michigan have stacked a second layer of transistors directly atop a state-of-the-art silicon chip.

They propose that their design could remove the need for a second chip that converts between high- and-low voltage signals, which currently stands between the low-voltage processing chips and the higher-voltage user interfaces.

“Our approach can achieve better performance in a smaller, lighter package,” said Becky Peterson, an associate professor of electrical engineering and computer science and project leader.

Moore’s Law holds that computing power per dollar doubles roughly every two years. As silicon transistors have shrunk in size to become more affordable and power efficient, the voltages at which they operate have also fallen.

Higher voltages would damage the increasingly small transistors. Because of this, state-of-the-art processing chips aren’t compatible with higher-voltage user interface components, such as touchpads and display drivers. These need to run at higher voltages to avoid effects such as false touch signals or too-low brightness settings.

“To solve this problem, we’re integrating different types of devices with silicon circuits in 3D, and those devices allow you to do things that the silicon transistors can’t do,” Peterson said.

Source: “Beyond Moore’s Law: Taking transistor arrays into the third dimension”, Katherine McAlpine, Nicole Casal Moore, University of Michigan