An EPFL lab, has come up with a new type of logic diagram and related optimization methods, that can be used to design computer chips with a nearly 20% gain in energy efficiency, speed or size. The lab has just entered into a license agreement with Synopsys, a global leader in electronic design automation and chip fabrication software.

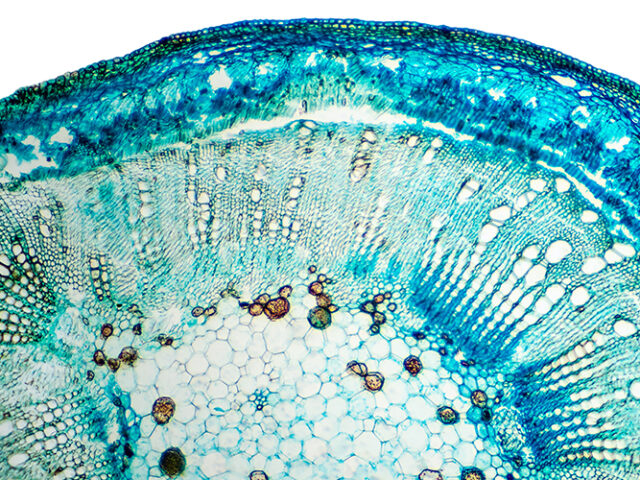

EPFL’s Integrated Systems Laboratory (LSI) has developed a method for reducing the power requirement of computer chips by mapping out their logic flows in an entirely new way. By using a different set of logic functions for the gates on the billions of transistors on electronic circuits, this system shortens the circuits’ calculation steps. That means chip designers can make their chips either smaller, faster or more energy efficient. Industry leader Synopsys has just acquired the rights to use the technology through a non-exclusive license agreement.

Streamed logic structures for more powerful chips

Today most engineers use electronic design automation software to design circuits. This software programs translate complex computational models into a labyrinth of billions of microscopic transistors. The LSI laboratory, directed by Giovanni De Micheli, has a longtime and worldwide renowned experience in design automation. There are only few companies and commercial products in use that sustain the entire semiconductor industry effort. Luca Amarù – while he was a PhD student at LSI – set out to radically change how design automation software generates logic diagrams in order to produce better designs.

Source: “EPFL lab develops method for designing lower-power circuits”, Cecilia Carron, EPFL